# Compact Model for Double-Gate Tunnel FETs With Gate–Drain Underlap

Peng Xu<sup>®</sup>, *Student Member, IEEE*, Haijun Lou<sup>®</sup>, *Member, IEEE*, Lining Zhang<sup>®</sup>, *Member, IEEE*, Zhonghua Yu, and Xinnan Lin, *Member, IEEE*

Abstract—A compact model for double-gate tunnel FETs (TFETs) with gate–drain underlap (DG u-TFET) is proposed which accounts for the alleviation of ambipolar current and Miller capacitance ( $C_{dg}$ ) compared with double-gate tunnel FETs (DG TFET). The oN-state current degradation caused by the underlap is reproduced by extending the ideal DG TFET model with an effective resistance between the channel and the drain. Based on the device surface potential, the terminal charge model is developed which enables the possibility of circuit simulation and the terminal capacitance is further derived from the definition. This model captures the electrical characteristics of DG u-TFET explicitly and good agreement is achieved compared with TCAD simulation. After the model is implemented into HSPICE, an inverter is established and successfully simulated without convergence problem.

Index Terms—Ambipolar current, compact model, gate–drain underlap, tunneling field-effect transistor (TFET).

#### I. INTRODUCTION

**C**ONTINUOUS downscaling of the conventional MOSFETs has brought the issue of device power dissipation more considerable. Recently, the tunneling fieldeffect transistor (TFET) has attracted much attention as efficient energy saving device due to its superior subthreshold

Manuscript received July 19, 2017; revised September 15, 2017; accepted October 11, 2017. Date of publication October 25, 2017; date of current version November 22, 2017. This work was supported in part by the National Science Funds of China under Grant 61504051, in part by the Shenzhen Key Laboratory Project under Grant ZDSYS20170303140513705, in part by the Guangdong National Science Funds under Grant 2015A030313851, and in part by the General Research Fund from the Research Grant Council of Hong Kong under Project 611012. The review of this paper was arranged by Editor H. Shang. *(Corresponding authors: Haijun Lou; Xinnan Lin.)*

P. Xu, Z. Yu, and X. Lin are with the Shenzhen Key Laboratory of Advanced Electron Device and Integration, School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen 518055, China (e-mail: 270257558@qq.com; xnlin@pkusz.edu.cn).

H. Lou is with the Shenzhen Key Laboratory of Advanced Electron Device and Integration, School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen 518055, China, and also with the School of Science, Lanzhou University of Technology, Lanzhou 730050, China (e-mail: louhj04@163.com).

L. Zhang is with the College of Electronic Science and Technology, Shenzhen University, Shenzhen 518060, China (e-mail: Inzhang@ieee.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2017.2762861

performance [1]–[5]. Nevertheless, to realize the application of TFET into circuit level, the ambipolar behavior should be well controlled [6]–[9]. Nowadays, the gate–drain underlap structure [10] has been effectively utilized in TFET (represented as u-TFET) to suppress the ambipolar current. Through simulation study, the feasibility of Miller capacitance ( $C_{dg}$ ) reduction compared with conventional TFET has been demonstrated by Zhuge *et al.* [11] and the range of underlap ratio ( $L_{underlap}/L_{channel}$ ) for device performance optimization has also been discussed in [12].

Some works on u-TFET continue in terms of performance estimation at circuit level by table look-up method. Vijayvargiya et al. [13] explored the analog/RF performance attributes of u-TFET for low-power applications. Avci et al. [14] compared the performance, switching energy, and process variations for u-TFET and MOSFET in logic. Biswas et al. [15] investigated the u-TFET as a capacitorless memory cell. In order to extend the huge potential of u-TFET in practical circuit implementation, a compact model available for SPICE is necessary. Recently, several TFET SPICE models have published [16]–[20]. Simultaneously, the impact of the gate-drain underlap has been found and studied by simulation, while not involved in model yet. Considering the accuracy requirement for circuit simulation, an SPICE compatible model for TFET with gate-drain underlap is urgently needed.

In this paper, a compact model for silicon-based doublegate TFETs with gate–drain underlap (DG u-TFET) that can be applied to all operation regions (positive/negative gate bias) is proposed for the first time. The description of ambipolar current is necessary due to the negative input from output voltage undershot (<0 V) [18] in multistage circuit. It is a complete model with both drain current and terminal charge/capacitance which is ready for circuit simulation. The model shows good accuracy compared with TCAD simulation and works properly in circuit simulator (HSPICE).

### II. DG u-TFET MODELING UNDER POSITIVE GATE BIAS

Similar to double-gate DG TFET, the DG u-TFET is equivalent to a gated tunnel diode in series with a gate-drain underlapped DG MOSFET. To comprehensively model the surface potential for DG u-TFET, one extra Poisson's equation (PE) should be solved for the underlap. Although subthreshold analysis for gate-drain underlapped MOSFET has

0018-9383 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

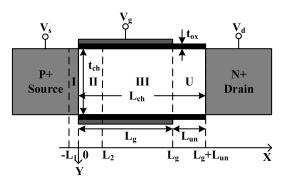

Fig. 1. Cross-sectional view of an n-type DG u-TFET. The gate dielectric is  $S_iO_2$ . The source and drain are heavily doped, while the channel is intrinsic.

been demonstrated [21]–[24], in the strong inversion condition, the PE in the underlap becomes unsolvable due to the nonuniform charge density. On the other hand, it has been reported that the underlap structure will increase the channel resistance and induce ON-state current degradation [10], [11]. Thus, a quantitative evaluation on the current degradation is needed for device performance optimization.

Instead of solving the PE, one possible way to consider the effect of the underlap is to model it as a series resistor, which is also applied in MOSFET modeling when the gate–source/drain underlap is introduced [25]–[27]. One main advantage of the resistor method is that it brings less extra computing burden than the coupling of DG TFET and DG underlapped MOSFET which is benefit for SPICE simulation. In the following work, it will be shown that by introducing a first-order resistor model, the ideal DG TFET model is extended for DG u-TFET, which reproduces the ON-state current degradation. Before this, a brief review on the surface potential model for DG TFET [17] is given below.

Fig. 1 shows the cross-sectional view of an n-type DG u-TFET. It is divided into four regions: source depleted region I, channel depleted region II, drift-diffusion region III, and underlap region U. Supposing that  $L_{un} = 0$ , the device is reduced to a DG TFET. After solving the PEs, the surface potential in region I and region II can be, respectively, expressed as

$$\varphi_{s1}(x) = \frac{qN_{\text{seff}}}{2\varepsilon_{\text{si}}}(x+L_1)^2 \tag{1}$$

$$\varphi_{s2}(x) = (V_{gs} - V_{fbs}) - [V_{gs} - V_{fbs} - V_{bi} - \varphi_{dg}] \times \cosh\left(\frac{x - L_2}{\lambda}\right)$$

(2)

where  $\varepsilon_{\rm si}$  is the relative permittivity of silicon,  $N_{\rm seff} = N_s - 2\varepsilon_{\rm ox}(V_{\rm gs} - V_{\rm fbs})/(qt_{\rm ox}t_{\rm ch}\pi/2)$  is the effective source doping concentration,  $V_{\rm fbs} = W_{\rm fgate} - W_{\rm fsource}$  is the flat band voltage,  $\lambda = (\varepsilon_{\rm si}t_{\rm ch}t_{\rm ox}/(2\varepsilon_{\rm ox}))^{1/2}$  is the natural length of double-gate MOSFET [28],  $V_{\rm bi}$  is the built-in potential of the source/channel junction, and  $\varphi_{\rm dg}$  is the surface potential in region III that calculated by the method in [29]. Detailed steps to come to the solution of the PE in each region and their corresponding boundary conditions can be found in [17]. By matching the boundary conditions, the lengths of region I

and II are further solved

$$L_1 = \sqrt{2\varepsilon_{\rm si}\varphi_s(0)/qN_{\rm seff}} \tag{3}$$

$$L_{2} = \lambda \cosh^{-1} \left[ -\frac{\varphi_{s}(0) - (V_{gs} - V_{fbs})}{(V_{gs} - V_{fbs}) - (V_{bi} + \varphi_{dg})} \right]$$

(4)

where  $\varphi_s(0) =$

$$\sqrt{[V_{\rm gs} - V_{\rm fbs} - (V_{\rm bi} + \varphi_{\rm dg})]^2 + 2(V_{\rm gs} - V_{\rm fbs})\Phi + \Phi^2} + (V_{\rm gs} - V_{\rm fbs} + \Phi), \quad \Phi = \frac{qN_{\rm seff}\lambda^2}{\varepsilon_{\rm si}}.$$

(5)

By finding the minimum tunneling distance in the light of the presented potential profile, the tunneling current can be further calculated using Kane's model [30]. Detailed procedures are also available in [17] and will not be further illustrated. Here, the ideal current for DG TFET is defined as  $I_{ds0}$ .

Now, supposing that  $L_{un} \neq 0$ , the underlap region behaves as a resistor. The effective resistance is given by a first-order model [31]

$$R_{\rm un} = \frac{L_{\rm un}}{q \cdot \mu_e \cdot n_{\rm un} \cdot W_g \cdot t_{\rm ch}} \tag{6}$$

where  $\mu_e$  is the electron mobility,  $n_{un}$  is the average electron concentration in the underlap region, and  $W_g$  is the width of the gate. For a given  $V_{gs0}$  and  $V_{ds0}$ , using ideal current  $I_{ds0}$  as initial solution, the voltage drop on the resistor is  $I_{ds0} \cdot R_{un}$ , which leads to the effective drain voltage for DG TFET:  $V_{ds,eff} = V_{ds0} - I_{ds0} \cdot R_{un}$ . Then, use  $I_{ds}(V_{gs0}, V_{ds,eff})$  to replace  $I_{ds0}$  and repeat the above process. Usually after two-three iterations, the drain current and the effective drain voltage will meet a convergence criterion for the final solution. As the effective drain voltage is obtained, surface potential for region I, II, and III (the DG TFET part) of DG u-TFET is also determined, which can be further used to calculate the terminal charge.

In device SPICE model, the terminal charge is needed for ac/transient simulation due to the charging and discharging process. Therefore, a terminal charge model for DG u-TFET is developed based on the aforementioned surface potential and the feasibility of expressing terminal charge in terms of terminal voltage has been verified [32]. Besides, the terminal capacitance is calculated by differentiating the terminal charge with respect to the terminal voltage, which reflects the impact of gate–drain underlap on the Miller capacitance.

Charge component of DG u-TFET includes charge in the source depletion region and the channel. Assuming that dopants are fully ionized, the depletion charge in region I can be calculated with

$$Q_s = -q N_{\text{seff}} W_g L_1. \tag{7}$$

The channel charge is divided into two parts: the inversion charge beneath the gate and the inner fringe charge [33]. Due to the poor coupling between the source and the gate, charge in the channel is entirely injected from the drain side [18]. Before the device is saturated, the inversion charge is dominant in the whole channel charge. The saturation here means drain current is saturated by increasing the drain voltage. Since the inversion charge in region II is ignored [17] and the inversion charge profile is approximately uniform before saturation, the total inversion charge can be calculated with Gauss's law

$$Q_{\rm ch_{inv}} = -2W_g t_{\rm ch} (L_g - L_2) C_{\rm ox} (V_{\rm gs} - V_{\rm fbs} - \varphi_{\rm dg} - V_{\rm bi}).$$

(8)

After the device is saturated, the inner fringing charge replaces the dominant role of the inversion charge. When the drain voltage is much higher than the gate voltage, electrons in the underlap region are almost depleted. This is different from DG TFET that only a narrow depletion forms near the channel/drain interface. In consequence, the maximum lateral electric field at the end of the channel can be approximated by

$$E_m = \frac{V_{\rm ds} + V_{\rm bi,d} - \varphi_{\rm dg}}{\lambda + L_{\rm un}} \tag{9}$$

where  $V_{\text{bi},d}$  is the built-in potential of the drain/channel junction. This expression guarantees the consistency between DG u-TFET and DG TFET when  $L_{\text{un}}$  equals to zero. With the zero-field assumption in region III [17], the inner fringe charge can be calculated with Gauss' law

$$Q_{\rm ch\_inf} = W_g t_{\rm ch} \varepsilon_{\rm si} E_m. \tag{10}$$

Therefore, the total channel charge is the summation of the two components

$$Q_{\rm ch} = Q_{\rm ch\_inv} + Q_{\rm ch\_inf}.$$

(11)

Due to the charge neutrality condition, charge in the gate terminal is

$$Q_g = -(Q_s + Q_{\rm ch}). \tag{12}$$

From the definition of terminal capacitance

$$C_{ij} = \frac{dQ_i}{dV_j} \tag{13}$$

the terminal capacitance  $C_{sg}$  and  $C_{dg}$  are given by

$$C_{\rm sg} = \frac{\partial Q_s}{\partial V_{\rm gs}}, \quad C_{\rm dg} = \frac{\partial Q_d}{\partial V_{\rm gs}} = \frac{\partial Q_{\rm ch}}{\partial V_{\rm gs}}.$$

(14)

Direct modeling for  $C_{sg}$  and  $C_{dg_{inf}}$  is also available to qualitatively understand the capacitance component

$$C_{\rm sg} = 2W_g \frac{\varphi_{\rm dg}}{V_{\rm gs} - V_{\rm fbs} - V_{\rm bi}} \frac{\varepsilon_{\rm si}t_{\rm ch}}{2\lambda} \exp\left(-\frac{N_{\rm seff}L_1}{N_s\lambda}\right) \quad (15)$$

$$C_{\rm dg\_inf} = 2W_g \exp\left[-\frac{q(V_{\rm gs} - V_{\rm fbs} - V_{\rm bi} - \varphi_{\rm dg})}{kT}\right] \\ \times \frac{2\varepsilon_{\rm si}}{\pi} \ln\left[1 + \frac{t_{\rm ch}}{2(t_{\rm ox} + L_{\rm un})} \sin\left(\frac{\pi}{2}\frac{\varepsilon_{\rm ox}}{\varepsilon_{\rm si}}\right)\right]. \quad (16)$$

## III. DG u-TFET MODELING UNDER NEGATIVE GATE BIAS

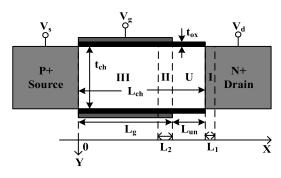

It has been illustrated that with gate-drain underlap, carrier tunneling rate under negative gate bias through channel/drain barrier decreases due to larger tunnel distance and reduced inside electric field [9]. In this condition, similar to Section II, DG u-TFET is divided into four regions (see Fig. 2): drain depleted region I, underlap region U, channel depleted region II, and drift-diffusion region III. In the following

Fig. 2. Cross-sectional view of DG u-TFET under negative gate bias.

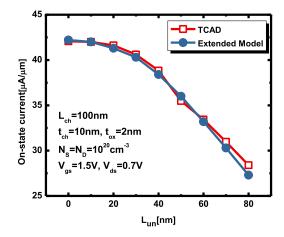

Fig. 3. Comparison between model-predicted on-state current and TCAD simulation by increasing  $L_{un}$  from 0 to 50 nm.

derivation, the surface potential is with reference to the channel Fermi level.

Due to the ultrathin body, potential along y-direction in region I and region U is assumed to be uniform. With the depletion approximation and neglecting the gate fringing field, surface potential in region I and region U can be calculated by solving the 1-D PE

$$\frac{d^2\varphi_{\rm sj}(x)}{dx^2} = -\frac{qN_j}{\varepsilon_{\rm si}} \tag{17}$$

where j = 1, u which refers to region I and region U, respectively. The general form solution for (17) is easily obtained by integrating twice. Substituting the boundary conditions

$$\varphi_{s1}(L_{ch} + L_1) = V_D, \quad \frac{d\varphi_{s1}(x)}{dx}|_{x=L_{ch}+L_1} = 0$$

(18)

where  $V_D = V_{bi,d} + V_{ds}$ , the surface potential in region I is solved as

$$\varphi_{s1}(x) = \frac{-qN_D}{2\varepsilon_{\rm si}}(x - L_{\rm ch} - L_1)^2 + V_D. \tag{19}$$

Likewise, the surface potential in region U is obtained by matching the boundary conditions at  $x = L_{ch}$

$$\varphi_{\rm su}(L_{\rm ch}) = \varphi_{s1}(L_{\rm ch}), \quad \frac{d\varphi_{\rm su}(x)}{dx}|_{x=L_{\rm ch}} = \frac{d\varphi_{s1}(x)}{dx}|_{x=L_{\rm ch}}$$

(20)

and its solution is

$$\varphi_{\rm su}(x) = \frac{-qN_D}{2\varepsilon_{\rm si}}L_1^2 + V_D - \frac{qN_D}{\varepsilon_{\rm si}}L_1(L_{\rm ch} - x). \tag{21}$$

Region II can be treated as a full-depletion region neglecting the inversion charge. Due to the double-gate structure, 2-D PE in region II is simplified with parabolic approximation [34] and transformed to the well-known form

$$\frac{d^2\varphi_{s2}(x)}{dx^2} - \frac{\varphi_{s2}(x) - (V_{gs} - V_{fbb})}{\lambda^2} = \frac{q \cdot N_{ch}}{\varepsilon_{si}}$$

(22)

where  $V_{\rm fbb} = W_{\rm fgate} - W_{\rm fbody}$  is the flat band voltage,  $N_{\rm ch}$  is the channel doping concentration, and  $\lambda = (\varepsilon_{\rm si} t_{\rm ch} t_{\rm ox} / (2\varepsilon_{\rm ox}))^{1/2}$  is the natural length of double-gate MOSFET. The general form solution for (22) is given by

$$\varphi_{s2}(x) = A \exp\left(\frac{x - (L_g - L_2)}{\lambda}\right) + B \exp\left(-\frac{x - (L_g - L_2)}{\lambda}\right) + (V_{gs} - V_{fbb}). \quad (23)$$

By substituting the boundary conditions at  $x = L_g - L_2$

$$\varphi_{s2}(L_g - L_2) = \varphi_s, \quad \frac{d\varphi_{s2}(x)}{dx}|_{x = L_g - L_2} = 0$$

(24)

where  $\varphi_s$  is the surface potential in region III that calculated by the method in [22], (23) is transformed to

$$\varphi_{s2}(x) = [\varphi_s - (V_{gs} - V_{fbb})] \cosh\left(\frac{x - (L_g - L_2)}{\lambda}\right) + (V_{gs} - V_{fbb}). \quad (25)$$

The lengths of region I and region II can be derived using the continuity of surface potential at the boundaries. In this way,  $L_1$  is calculated by solving the quartic equation as follows:

$$(V_D - V_{gs} + V_{fbb} - q N_D L_1 L_u / \varepsilon_{si} - q N_D / (2\varepsilon_{si}) L_1^2)^2 - (q N_D / \varepsilon_{si} L_1 \lambda)^2 = (\varphi_s - V_{gs} + V_{fbb})^2.$$

(26)

Because no analytical solution is available,  $L_1$  is solved numerically, which can further lead to the length of region II

$$L_{2} = \lambda \cosh^{-1} \left\{ \frac{V_{D} - \frac{qN_{D}}{\varepsilon_{\rm si}} L_{1} L_{u} - (V_{\rm gs} - V_{\rm fbb}) \frac{qN_{D}}{2\varepsilon_{\rm si}} L_{1}^{2}}{\varphi_{s} - V_{\rm gs} + V_{\rm fbb}} \right\}.$$

(27)

To obtain the minimum tunneling distance, it is vital to judge where the tunneling takes place. At low  $|V_{gs}|$ , the tunneling distance is relatively large and the carriers may tunnel from region I to region II. In this condition,  $W_{t,min}$  is found to be

$$W_{t,\min} = X_1 - X_2$$

(28)

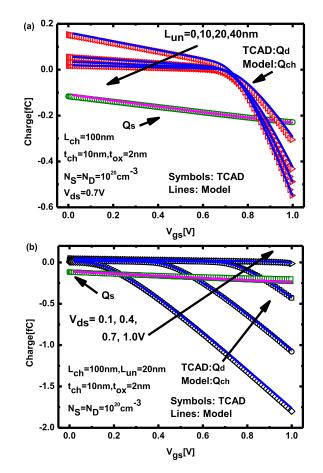

Fig. 4. Model-predicted charges versus TCAD simulation. (a) Predicted channel charge is identical with the simulated drain charge. (b) Charge components are compared from saturation to nonsaturation condition.

where (29)–(31), as shown at the bottom of the this page,  $X_1$  and  $X_2$  is the tunneling position in region I and region II, respectively, and  $E_{gq} = E_g/q$ . When  $X_2$  is greater than  $L_g$ , tunneling occurs between region I and region U, and  $W_{t,\min}$  is reduced to

$$W_{t,\min} = \frac{E_{gq}}{qN_D L_1} \varepsilon_{\rm si}.$$

(32)

According to Kane's model, the peak tunneling generation rate is written as

$$G_{\text{tun,max}} = A \cdot \frac{E_g^{3/2}}{q^2} \cdot \frac{1}{W_{t,\min}^2} \exp\left(-\frac{W_{t,\min}}{\lambda_{\text{tun}}}\right)$$

(33)

$$X_{1} = L_{\rm ch} + L_{1} - \sqrt{\frac{2\varepsilon_{\rm si}(V_{D} - \psi_{I} - E_{gq})}{qN_{D}}}$$

(29)

$$X_2 = \lambda \cosh^{-1} \left( \frac{\psi_I - V_{gs} + V_{fbb}}{\varphi_s - V_{gs} + V_{fbb}} \right) + L_g - L_2$$

(30)

$$\psi_{I} = V_{gs} - V_{fbb} + \frac{q \lambda N_{D}}{\varepsilon_{si}} + \sqrt{\left(\frac{q \lambda^{2} N_{D}}{\varepsilon_{si}}\right)^{2} + (V_{gs} - V_{fbb} - \varphi_{s})^{2} + \frac{2q \lambda^{2} N_{D}}{\varepsilon_{si}} (V_{D} - V_{gs} + V_{fbb} - E_{gq})}$$

(31)

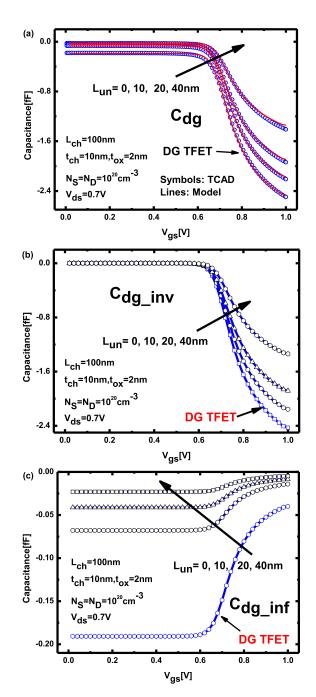

Fig. 5. (a) Model-predicted capacitance versus TCAD simulation with different  $L_{un}$ . (b) and (c) show the tendency that  $C_{dg_{inv}}$  and  $C_{dg_{inf}}$  change with increasing  $L_{un}$ .

where  $\lambda_{tun} = 1/(q \cdot B \cdot E_g^{1/2})$ , and drain current is then calculated by integrating the electron tunneling generation rate from  $X = -\infty$  to  $X = +\infty$

$$I_{\rm ds,amb} = \frac{2W_g t_{\rm ch} G_{\rm tun,max}}{B\sqrt{E_{gq}}}.$$

(34)

A correction factor (35) of Fermi level is multiplied to (34) to avoid the nonzero current at  $V_{ds} = 0$  and guarantee the current continuity

$$f_{\text{fermi}} = 2\left\{\frac{1}{2} - 1/\left[1 + \exp\left(\frac{q V_{\text{ds}}}{f_n \cdot kT}\right)\right]\right\}.$$

(35)

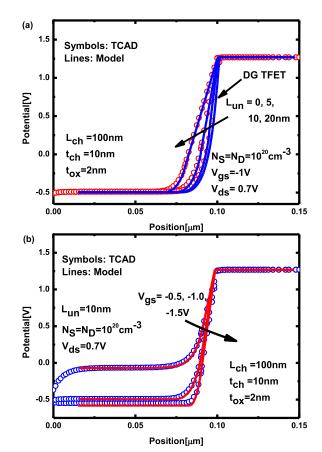

Fig. 6. Model-predicted surface potential versus TCAD simulation in negative gate bias condition. (a) Different  $L_{un}$ . (b) Different  $V_{gs}$  at  $L_{un}$ =10nm.

#### **IV. RESULTS AND DISCUSSION**

The model-predicted values are compared with TCAD simulation for validation. The device simulation setup includes dynamic nonlocal path band to band tunneling model, Shockley–Read–Hall recombination model, and Fermi statistics. Device parameters are consistent for all groups of simulation except  $L_{un}$ .

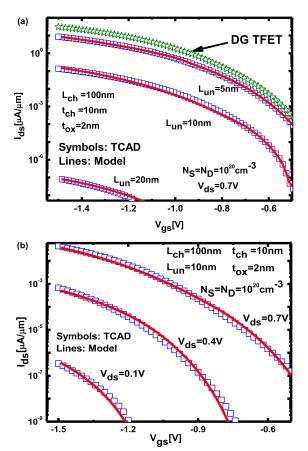

The ON-state current degradation of DG u-TFET varying the underlap distance is shown in Fig. 3 and it is seen to reproduce the current degradation with an acceptable accuracy. This extended model indicates that the current degradation is related to both the ideal current  $I_{ds0}$  and the underlap distance  $L_{un}$ . On the one hand, larger  $L_{un}$  brings bigger series resistance so that drain voltage drops more on the underlap; on the other hand, if  $I_{ds0}$  is originally very large, like in heterojunction TFETs (H-TFET) or the applied gate voltage is very high, higher voltage drop is also expected on the underlap. For H-TFETs, this degradation can be evident even at a small gate voltage.

The terminal charge of DG u-TFET is plotted in Fig. 4. Fig. 4(a) shows that, compared with DG TFET, when increasing the underlap distance, the gate length is diminished thus reducing the effective area for inversion charge. The maximum electric field near the drain side becomes smaller that the inner fringe charge is also reduced. However, the source charge is barely affected by the gate–drain underlap, as the source depletion width mainly depends on the doping profile.

Fig. 7. Model-predicted ambipolar current versus TCAD simulation. (a) Different  $L_{un}$ . (b) Different  $V_{ds}$  at  $L_{un}$ =10nm.

Fig. 4(b) clearly shows the inversion electrons faded by increasing the drain voltage, thus the device works from nonsaturation to saturation region. The model-predicted gate-drain capacitance ( $C_{dg}$ ) is compared with simulation data at different  $L_{un}$  in Fig. 5(a). At each underlap distance, the model matches the simulation data very well. The total gate-drain capacitance is decreased with  $L_{un}$ , and its two components  $C_{dg_{inv}}$  and  $C_{dg_{inf}}$  are plotted in Fig. 5(b) and (c). At each operation region, like the channel charge, only one component is dominant. As it can be seen, in saturation region, the inversion layer cannot be generated that  $C_{dg_{inv}} = 0$ . The inner fringe capacitance is also decreased when the device goes into nonsaturation by increasing  $V_{gs}$ .

The surface potential and ambipolar current are checked for DG u-TFET with  $L_{un} = 5$ , 10, 20 nm. Also, profiles of DG TFET are also plotted for comparison. As shown in Fig. 6, the model-predicted potential is well matched with the TCAD simulation, proving the correctness of full-depletion assumption in region U. As  $L_{un}$  is increased, potential slopes more gently through the underlap region, reducing the inside electric field, thus the carrier tunneling rate is effectively diminished. Since the observed ambipolar current is pretty small and ranges from several orders, the simulation and model-predicted results are extracted from  $V_{gs} = -0.5$  V where significant current can be reached. Fig. 7(a) shows that current reduction with more than six orders of magnitude is achieved as the underlap distance is increased from 0 to 20 nm at  $V_{gs} = -1.5$  V. With a 20-nm underlap, the ambipolar current is almost

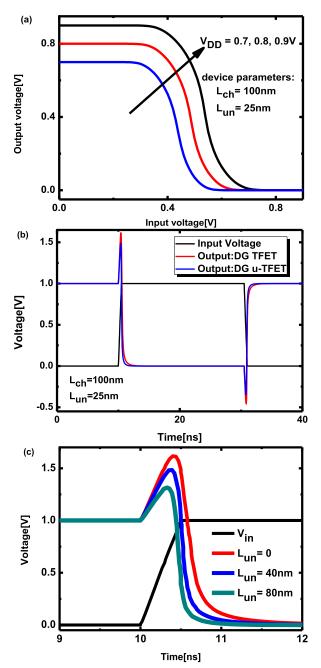

Fig. 8. (a) VTCs of DG u-TFET inverter. (b) Transient response of DG TFET inverter and DG u-TFET inverter. (c) Output voltage overshot (undershot) is alleviated by increasing underlap.

negligible under the common operation voltage ( $V_{DD} \sim 0.7 \text{ V}$ ) as the output voltage undershot is always smaller than  $-V_{DD}$ . Generally, as shown by the simulation and model results, shorter gate will bring smaller gate–drain capacitance and is more effective for suppressing the ambipolarity, but mean-while, more drain current degradation. Thus, moderation must be taken, according to the real circuit requirement.

To demonstrate the model flexibility in circuit simulation, it is coded with Verilog-A and implemented into HSPICE. For the sake of simplicity, an inverter is established, and its voltage transfer curves (VTCs) at different supply voltages are shown in Fig. 8(a). Transient response with  $V_{DD} = 0.9$  V and a load capacitance  $C_{load} = 1$  fF is shown in Fig. 8(b). The output voltage over/undershot is alleviated in DG u-TFET inverter due to the reduced Miller capacitance [Fig. 8(c)]. There is no convergence problem during the simulation process, demonstrating the model's robustness in the running process.

## V. CONCLUSION

A compact model for DG u-TFET in all operation regions is proposed which reflects the characteristics of the gate–drain underlap on device drain current and Miller capacitance. According to the simulation results of TCAD and HSPICE, the model shows acceptable accuracy and flexibility in circuit simulation. This model provides constructive guidelines to design the gate–drain underlap for TFET and can be further applied to circuit evaluation on the performance boost due to the diminished ambipolar current and Miller capacitance. It is possible that via this model, subsequent works on u-TFET-based circuits will be carried out for future applications.

## REFERENCES

- [1] C. Hu *et al.*, "Prospect of tunneling green transistor for 0.1 V CMOS," in *IEDM Tech. Dig.*, Dec. 2010, pp. 16.1.1–16.1.4, doi: 10.1109/IEDM.2010.5703372.

- [2] A. C. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proc. IEEE*, vol. 98, no. 12, pp. 2095–2110, Dec. 2010, doi: 10.1109/JPROC.2010.2070470.

- [3] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 743–745, Aug. 2007, doi: 10.1109/LED.2007.901273.

- [4] R. Jhaveri, V. Nagavarapu, and J. C. S. Woo, "Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 80–86, Jan. 2011, doi: 10.1109/TED.2010.2089525.

- [5] J. Appenzeller, Y.-M. Lin, J. Knoch, and P. Avouris, "Band-to-band tunneling in carbon nanotube field-effect transistors," *Phys. Rev. Lett.*, vol. 93, no. 19, pp. 196805-1–196805-4, Nov. 2004, doi: 10.1103/.Phys-RevLett.93.196805.

- [6] T. Krishnamohan, D. Kim, S. Raghunathan, and K. Saraswat, "Doublegate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and ≪60 mV/dec subthreshold slope," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–3, doi: 10.1109/IEDM.2008.4796839.

- [7] K. Boucart and A. M. Ionescu, "Double-gate tunnel FET with highκ gate dielectric," *IEEE Trans. Electron Devices*, vol. 54, no. 7, pp. 1725–1733, Jul. 2007, doi: 10.1109/.TED.2007.899389.

- [8] J. Wan, C. Le Royer, A. Zaslavsky, and S. Cristoloveanu, "SOI TFETs: Suppression of ambipolar leakage and low-frequency noise behavior," *Proc. Eur. Solid-State Device Res. Conf.*, Sep. 2010, pp. 341–344, doi: 10.1109/ESSDERC.2010.5618222.

- [9] A. Hraziia, A. Vladimirescu, A. Amara, and C. Anghel, "An analysis on the ambipolar current in Si double-gate tunnel FETs," *Solid-State Electron.*, vol. 70, pp. 67–72, Apr. 2012, doi: 10.1016/j.sse.2011.11.009.

- [10] A. S. Verhulst, W. G. Vandenberghe, K. Maex, and G. Groeseneken, "Tunnel field-effect transistor without gate-drain overlap," *Appl. Phys. Lett.*, vol. 91, no. 5, p. 053102, 2007, doi: 10.1063/1.2757593.

- [11] J. Zhuge *et al.*, "Digital-circuit analysis of short-gate tunnel FETs for low-voltage applications," *Semicond. Sci. Technol.*, vol. 26, p. 085001, Apr. 2011, doi: 10.1088/0268-1242/26/8/085001.

- [12] J. S. Lee *et al.*, "Simulation study on effect of drain underlap in gate-allaround tunneling field-effect transistors," *Current Appl. Phys.*, vol. 13, pp. 1143–1149, Aug. 2013, doi: 10.1016/j.cap.2013.03.012.

- [13] V. Vijayvargiya, B. S. Reniwal, P. Singh, and S. K. Vishvakarma, "Analogue/RF performance attributes of underlap tunnel field effect transistor for low power applications," *Electron. Lett.*, vol. 52, no. 7, pp. 559–560, 2016, doi: 10.1049/el.2015.3797.

- [14] U. E. Avci, R. Rios, K. Kuhn, and I. A. Young, "Comparison of performance, switching energy and process variations for the TFET and MOSFET in logic," in *Symp. VLSI Technol. Dig. Tech. Papers*, 2011, pp. 124–125.

- [15] A. Biswas *et al.*, "Investigation of tunnel field-effect transistors as a capacitor-less memory cell," *Appl. Phys. Lett.*, vol. 104, no. 9, p. 092108, 2014, doi: 10.1063/1.4867527.

- [16] Y. Hong, Y. Yang, L. Yang, G. Samudra, C.-H. Heng, and Y.-C. Yeo, "SPICE behavioral model of the tunneling field-effect transistor for circuit simulation," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 12, pp. 946–950, Dec. 2009, doi: 10.1109/TCSII.2009.2035274.

- [17] L. Zhang and M. Chan, "SPICE modeling of double-gate tunnel-FETs including channel transports," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 300–307, Feb. 2014, doi: 10.1109/TED.2013.2295237.

- [18] L. Zhang, X. Lin, J. He, and M. Chan, "An analytical charge model for double-gate tunnel FETs," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3217–3223, Dec. 2012, doi: 10.1109/TED.2012.2217145.

- [19] C. Tanaka, K. Adachi, M. Fujimatsu, A. Hokazono, Y. Kondo, and S. Kawanaka, "Implementation of TFET SPICE model for ultra-low power circuit analysis," *IEEE J. Electron Devices Soc.*, vol. 4, no. 5, pp. 273–277, Sep. 2016, doi: 10.1109/JEDS.2016.2550606.

- [20] H. Lu, W. Li, Y. Lu, P. Fay, T. Ytterdal, and A. Seabaugh, "Universal charge-conserving TFET SPICE model incorporating gate current and noise," *IEEE J. Explor. Solid-State Computat. Devices Circuits*, vol. 2, pp. 20–27, 2016, doi: 10.1109/.JXCDC.2016.2582204.

- [21] A. Kranti and G. A. Armstrong, "Engineering source/drain extension regions in nanoscale double gate (DG) SOI MOSFETs: Analytical model and design considerations," *Solid-State Electron.*, vol. 50, pp. 437–447, 2006, doi: 10.1016/j.sse.2006.02.012.

- [22] R. Vaddi, R. P. Agarwal, and S. Dasgupta, "Analytical modeling of subthreshold current and subthreshold swing of an underlap DGMOSFET with tied–independent gate and symmetric-asymmetric options," *Microelectron. J.*, vol. 42, no. 5, pp. 798–807, 2011, doi: 10.1016/j.mejo.2011.01.004.

- [23] L. Zhang, C. Ma, J. He, X. Lin, and M. Chan, "Analytical solution of subthreshold channel potential of gate underlap cylindrical gate-allaround MOSFET," *Solid-State Electron.*, vol. 54, no. 8, pp. 806–808, 2010, doi: 10.1016/j.sse.2010.03.020.

- [24] V. Kumari, K. Sharmetha, M. Saxena, and M. Gupta, "Underlapped FinFET on insulator: Quasi3D analytical model," *Solid-State Electron.*, vol. 129, pp. 138–149, Mar. 2017, doi: 10.1016/j.sse.2016.11.013.

- [25] A. Dixit, A. Kottantharayil, N. Collaert, M. Goodwin, M. Jurczak, and D. De Meyer, "Analysis of the parasitic S/D resistance in multiple-gate FETs," *IEEE Trans. Electron Devices*, vol. 52, no. 6, pp. 1132–1140, Jun. 2005, doi: 10.1109/.TED.2005.848098.

- [26] D. Tekleab, S. Samavedam, and P. Zeitzoff, "Modeling and analysis of parasitic resistance in double-gate FinFETs," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2291–2296, Oct. 2009, doi: 10.1109/TED.2009.2028377.

- [27] N. Paydavosi et al., "BSIM—SPICE models enable FinFET and UTB IC designs," IEEE Access, vol. 1, pp. 201–215, 2013, doi: 10.1109/ACCESS.2013.2260816.

- [28] R.-H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: From bulk to SOI to bulk," *IEEE Trans. Electron Devices*, vol. 39, no. 7, pp. 1704–1710, Jul. 1992, doi: 10.1109/ACCESS.2013.2260816.

- [29] T. Yuan, X. Liang, W. Wang, and H. Lu, "A continuous, analytic draincurrent model for DG MOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 2, pp. 107–109, Feb. 2004, doi: 10.1109/.LED.2003.822661.

- [30] P. M. Solomon *et al.*, "Universal tunneling behavior in technologically relevant P/N junction diodes," *J. Appl. Phys.*, vol. 95, no. 10, pp. 5800–5812, 2004, doi: 10.1063/1.1699487.

- [31] M. M. Chowdhury, "Physical analysis, modeling, and design of nanoscale double-gate MOSFETs with gate-source/drain underlap," Ph.D. dissertation, Dept. Elect. Comput. Eng., Univ. Florida, Gainesville, FL, USA, 2006.

- [32] A. C. T. Aarts, R. van der Hout, J. C. J. Paasschens, A. J. Scholten, M. B. Willemsen, and D. B. M. Klaassen, "New fundamental insights into capacitance modeling of laterally nonuniform MOS devices," *IEEE Trans. Electron Devices*, vol. 53, no. 2, pp. 270–278, Feb. 2006, doi: 10.1109/TED.2005.862235.

- [33] S. Agrawal and J. G. Fossum, "A physical model for fringe capacitance in double-gate MOSFETs with non-abrupt source/drain junctions and gate underlap," *IEEE Trans. Electron Devices*, vol. 57, no. 5, pp. 1069–1075, May 2010, doi: 10.1109/.TED.2010.2044266.

- [34] R. Vishnoi and M. J. Kumar, "2-D analytical model for the threshold voltage of a tunneling FET with localized charges," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3054–3059, 2014, doi: 10.1109/.TED.2014.2332039.

Authors' photographs and biographies not available at the time of publication.